文|半導體產業縱橫

到2024年,使用RISC-V內核的SoC數量將達到20億。

近日,在加州聖克拉拉舉行的RISC-V 峯會上,包括 Andes Technology、RISC-V International、Arteris 和 Codasip 在內的四家公司發布了重要聲明。為期兩天的峯會為快速發展的 RISC-V 技術社區提供了一個教育、信息和討論的論壇。

RISC-V 峯會上的小組成員

RISC-V International 首席執行官 Calista Redmond 在開幕主題演講中表示,到 2024 年,使用 RISC-V 內核的 SoC 數量將達到 20 億,到 2031 年將增長到 200 億。為了驗證這一說法,Nvidia多媒體架構副總裁 Frans Sijstermans 在演講中表示,Nvidia 很可能在 2024 年出貨超過 10 億台使用 RISC-V 內核的設備。

晶心科技投資汽車安全

展會上,晶心科技推出全新車用RISC-V處理器AndesCore D45-SE,瞄準ISO 26262 ASIL-D(汽車安全完整性等級D)認證。

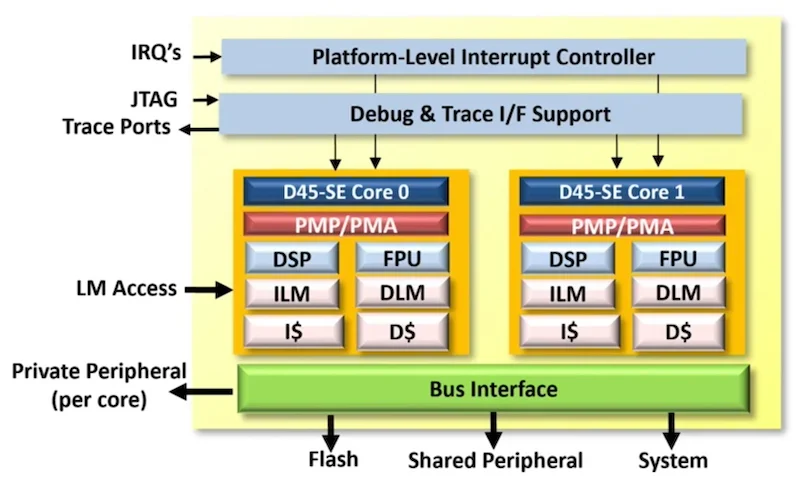

AndesCore D45-SE 框圖

AndesCore D45-SE 是一款 32 位、八級和雙發射 RISC-V 處理器。該芯片是生產中的 D45 處理器的衍生產品,經過增強以適應汽車應用。該處理器支持 RISC-V GCBP 擴展,包括單/雙精度浮點單元、16 位壓縮、位操作和打包 SIMD/DSP 擴展。

該設計還配備了 Andes 擴展和安全功能,以滿足認證要求。這些功能包括額外的處理器核心和用於自我診斷的比較器、ECC 內存錯誤校正、總線保護和硬件堆棧保護。D45-SE 的基準測試為 6.12 Coremark/MHz, 可以獨立運行其兩個核心,以提高可靠性和安全性。

D45-SE 處理器經過認證,可用於毫米波雷達傳感器、環視監控系統 (AVMS)、車輛儀表盤、動力總成 DCU、信息娛樂 DCU 以及前/後差速應用等關鍵應用。

RISC-V International 使用 RVA23 標準化 64 位

RISC-V 國際組織宣佈批准64 位 RISC-V 實施配置文件標準RVA23。RVA23配置文件具有針對數學密集型工作負載(例如人工智能/機器學習 (AI/ML)、加密、企業硬件系統和操作系統)的矢量擴展。這些新功能是使 RISC-V 成為更苛刻環境中可行選項的舉措的一部分。

雖然 RISC-V 在處理器架構設計方面提供了靈活性,但這種靈活性可能會帶來兼容性問題。配置文件可確保 RISC-V 指令集架構 (ISA) 的不同供應商實現之間的硅片通用性和軟件兼容性。RVA23 配置文件針對 64 位 RISC-V 實現了這一點。軟件可移植性對於 RISC-V 作為可行的行業處理器架構的發展至關重要。雖然所有 RISC-V 處理器都具有一些基本架構通用性,但該規範包括基礎架構和許多潛在擴展。配置文件指定了一組強制擴展,所有軟件開發人員都可以假設這些擴展將存在。非強制擴展允許針對特定應用程序進行定製,而不會影響核心標準功能。

除了數學密集型的矢量擴展之外,RVA23 還附帶了提供虛擬化功能的虛擬機管理程序擴展——這是企業和雲計算實施的關鍵要求。

Arteris 與 SiFive 合作開發 RISC-V SoC IP

Arteris 宣佈將SiFive P870-D RISC-V CPU 添加到其片上系統 (SoC) IP 庫中。對於尋求滿足高性能應用需求的數據中心硬件開發人員來說,經過預先驗證的解決方案可降低設計風險。Arteris SoC 基於其專有的可擴展緩存一致性片上網絡 (NoC) 互連 IP。高速 NoC IP 可降低 SoC 中處理單元之間的延遲。通過將 SiFive RISC-V IP 與 Arteris 技術相結合,SoC 開發人員擁有了經過預先驗證的高性能 RISC-V 核心選項。

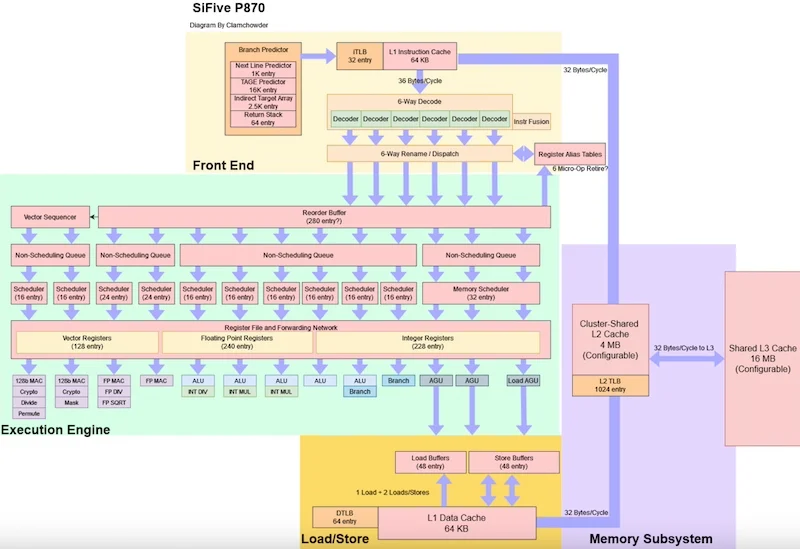

SiFive P870 的管道圖

Arteris/SiFive 產品支持高級微控制器總線架構 (AMBA) 一致性集線器接口 (CHI) 協議。AMBA CHI 是許多 SoC 解決方案使用的芯片互連規範的開放標準。SoC 通常是數據中心集羣系統的擴展仲裁器。高速 AMBA CHI 兼容互連架構和 RISC-V 核心將數據中心目標 SoC 開發帶入 RISC-V 生態系統。藉助內置支持,芯片設計人員可以確保最終結果具有數據中心構建的熟悉性、兼容性和互操作性。

Codasip 捐贈 RISC-V CHERI SDK

Codasip 宣佈將其 CHERI 軟件開發工具包 (SDK) 捐贈給社區利益組織 CHERI Alliance。功能硬件增強型 RISC 指令 (CHERI) 是一種安全技術,可保護系統免受基於指針的內存攻擊。據 Codasip 稱,過去 20 年,內存攻擊約佔網絡攻擊的 70%。

CHERI 架構擴展了標準 RISC-V 處理器指令集架構 (ISA),以解決 C 語言指針的漏洞。CHERI 用在不同的軟件功能之間具有明確界限的替代方案替換指針。通過隔離和替換指針,CHERI 可以顯著降低 C 和 C++ 代碼對基於指針的內存攻擊的脆弱性。

CHERI 最初是作為劍橋大學和 SRI International 的聯合研究項目開發的。此後,它獲得了美國國防高級研究計劃局 (DARPA)、英國研究與創新局 (UKRI) 和其他組織的資助。Codasip 於 2023 年發布了一款與 CHERI 兼容的可授權處理器。在此最新舉措中,Codasip 已將其 CHERI SDK 捐贈給 CHERI 聯盟,以確保 RISC-V 開發者社區能夠獲得更大的可用性。該 SDK 可在CHERI Alliance GitHub 網站上下載。