於NAND方面,甚至在包括NAND和DRAM在內的存儲方面,SK海力士過去多年無論是在技術還是市場份額一直以來都是落後於韓國競爭對手三星。

但據韓媒Businesskorea在10月底的報道透露,得益於在HBM上的成功,SK 海力士半導體業務部門的年度營業利潤將首次領先於 。這一發展標誌着全球半導體行業競爭格局的重大轉變,三星在該行業傳統上佔據主導地位。(具體細節可以參考我們之前的文章《韓國芯片,變天了》)

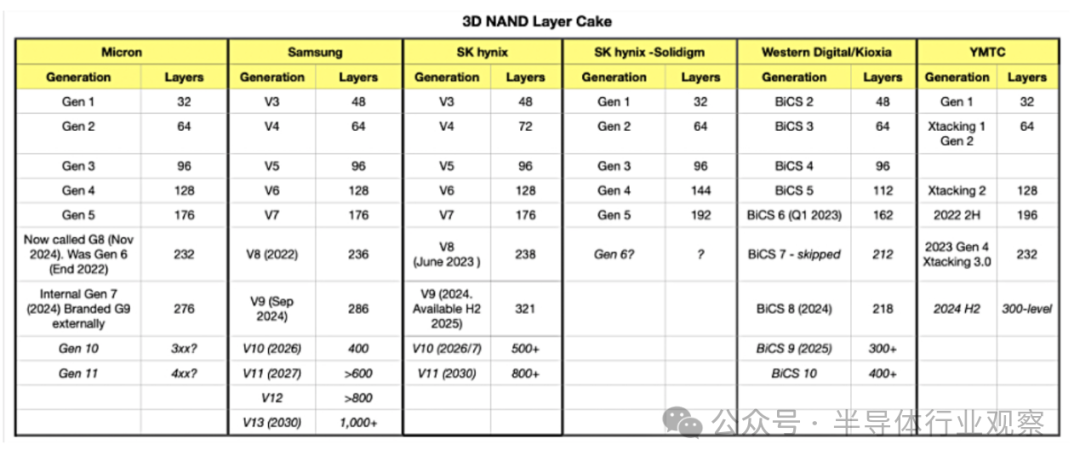

但現在,三星的另一個固有陣地NAND,也正在面臨SK海力士的衝擊。作為NAND 市場的領導者,據相關報告披露,截止2024年二季度,三星佔有NAND市場 36.9% 的份額。但作為追逐者的SK海力士(涵括SK Hynix 和 Solidigm ),其在全球NAND市場的份額從2020年的11.7%增長到2024年第二季度的22.5%。報告進一步指出,如果這一趨勢持續下去,單純SK海力士的年市場份額預計將在 2024 年首次超過 20%。

在新的NAND發布之後,SK海力士打出了追逐三星的重要一槍。

321層TLC NAND閃存,首超三星

據韓媒上月的報道,SK Hynix 啱啱超越了競爭對手三星。這家全球第二大內存芯片製造商已成為業內第一家量產 321 層三層單元 NAND 的公司。這一進步將以實惠的價格實現更高容量的內存。

SK Hynix 最近發布了其新的 1 兆位 4D NAND 芯片,創下了新紀錄。該公司勢頭強勁,不到一年前它還率先推出了 238 層 NAND。與之前的發布一樣,321 層的突破意義重大,因為它可以顯著提高消費者和企業 SSD 的存儲密度。

密集排列的芯片可能使容量超過 100TB 的 SSD 價格更便宜。這種 NAND 將特別適用於人工智能數據中心,儘管其他需要高能效存儲且性能要求高的應用也應該會從中受益。

SK Hynix 利用巧妙的工藝優化,將 300 多個層塞入單個 NAND 中。該公司的新「Three Plugs」技術通過優化的電氣連接工藝同時連接三個存儲層垂直通道。該工藝以出色的製造效率而聞名,並利用具有自動對準校正功能的低應力材料。

然而,連接所有這些層會產生應力和對準問題,SK Hynix 必須克服這些問題。該公司通過開發新的低應力材料和自動對準校正來克服這一問題,以便在製造過程中保持一切井然有序。

新工藝還通過重複使用與 238 層 NAND 相同的平台,將生產效率與上一代產品相比提高了59%。這些效率改進意味着市場上性能更佳、成本更低。該公司聲稱,與 238 層 NAND 相比,新的 321 層芯片的數據傳輸速度提高了 12%,讀取速度提高了 13%,能效提高了 10% 以上。

SK 海力士計劃逐步擴大 321-high 產品的使用範圍,瞄準需要低功耗和高性能的新興人工智能 (AI) 應用。SK 海力士 NAND 開發主管 Jungdal Choi 表示,這一進步使該公司更接近引領 AI 存儲市場,其中包括用於 AI 數據中心和設備上 AI 的固態硬盤 (SSD)。他指出,SK 海力士正在通過擴大其在超高性能 NAND 領域的產品組合以及以高帶寬內存 (HBM) 為主導的 DRAM 業務,向成為綜合 AI 內存提供商的方向邁進。

韓媒Chosun Biz指出,雖然 SK 海力士在 NAND 市場份額方面仍落後於三星,但它在垂直堆疊單元技術方面處於領先地位,這表明 NAND 市場可能會發生重大變化。

面對這個發布,三星強勢回擊。

三星正在開發 400 多層 3D NAND

據消息報道,三星目前正在開發286 層的第九代 3D NAND ,並正在開發 400 層技術。這是通過 2025 年 IEEE 國際固態電路會議議程發布透露。

據介紹,這款 1 兆位 NAND 芯片的密度為 28 Gb/mm2,層數超過 400 層,採用三級單元 (3b) 格式,將成為三星 V-NAND 技術的第十代產品。第九代芯片採用雙串堆疊,有 2 x 143 層,有 TLC 和QLC(4 位/單元)兩種格式。第九代 V-NAND 支持高達 3.2 Gbps 的數據速度,而新的 400 層以上技術則支持每針 5.6 Gbps,速度提高了 75%。該速度似乎既適合 PCIe 5,也適合兩倍快的 PCIe 6 互連。

在400層的NAND上,預計將採用三層堆棧架構,而不是當前的雙層堆棧設計。這一進步充分利用了三星在層數方面的領先優勢,因為它是唯一一家能夠在單個堆棧中生產超過 160 層的公司,而競爭對手只能達到 120-130 層。如果三星選擇三層堆棧方法,該公司可以實現驚人的 480 層。

其中,「WF-Bonding」則是三星實現這個層數的關鍵技術。據介紹,這是一項名為晶圓到晶圓鍵合的技術,其中兩個單獨的 NAND 晶圓(其上已製造單元和/或電路)相互連接。這種鍵合使每個晶圓的製造工藝在可擴展性、性能和產量方面得到優化。

三星表示,這種方法將實現具有大存儲容量和出色的硬盤性能的「超高」NAND 堆棧,非常適合 AI 數據中心的超高容量固態硬盤 (SSD)。據該公司稱,這款芯片被被稱為鍵合垂直NANDFlash,或BV NAND,是「人工智能的夢幻NAND」。

2013年,三星率先推出V NAND芯片,推出垂直垂直存儲單元——這是一個完整的產品。據三星稱,其BV NAND單位面積密度提高1.6倍。

三星計劃於 2027 年推出 V11 NAND,進一步開發其速度驚人的技術,將數據輸入和輸出提高 50%。該公司還計劃推出SSD訂閱服務,面向希望管理高昂AI半導體投資成本的科技公司。

除了400層NAND之外,三星電子明年還將增加其先進產品線的產量,雙重回應。該公司計劃在平澤園區安裝新的第9代(286層)生產設施,月產能為30,000至40,000片晶圓。此外,在中國西安工廠,三星將繼續將128層(V6)NAND生產線轉換為236層(V8)產品工藝。

其他廠商的亦步亦趨

由於分層競爭激烈,預計2025年NAND時代將進入400層,2027年將達到1000層。韓國業內專家認為,三星、SK海力士、美光等都將在2025年推出400層NAND產品。至於1000層NAND ,也是包括鎧俠在內所有NAND廠商的目標。

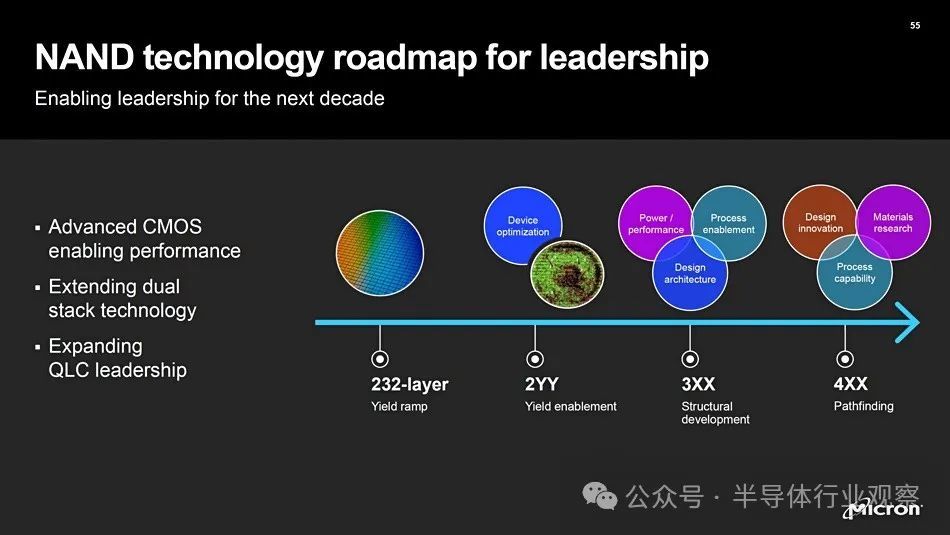

首先看美光方面,早在2022年,他們就發布了將NAND層數增加到 400 層以上的路線圖。

據報道,在這個產品中,他們將使用雙堆疊技術——是指將兩個 3D NAND 芯片堆疊在一起,即所謂的「串堆疊」。這克服了半導體制造中的難題,例如隨着層數的增加,需要在層間蝕刻連接孔。隨着孔深度的加深,這些孔的側面可能會變形,並阻止 NAND 單元正常運行。

美光表示,其重點是 QLC(4 位/單元)NAND,但並未提及使用PLC(五級單元)將單元位數增加到 5 ,西部數據正在研究此技術,Soldigm 正在開發。我們認為這是因為美光很謹慎,而不是因為 PLC NAND 不可行而拒絕了它。

西部數據則認為,層數稍高並不具有內在優勢,因為它正在橫向縮小單元尺寸(寬度和長度),並通過增加層數來增加芯片高度。這兩種技術的結合意味着它可以將芯片密度提高到與競爭對手相同或更高的程度,並且層數更少。

往下走,1000層也成為了廠商的目標。

例如鎧俠在今年於首爾舉行的國際內存技術研討會上表示,公司制定了雄心勃勃的路線圖,到 2027 年實現驚人的 1,000 層 3D NAND 閃存。三星之前也曾表示,計劃在 2030 年之前開發出層數超過 1,000 層的 NAND,但要實現這一目標絕非易事。

據日本媒體 PC Watch報道, Kioxia 的預測是基於過去的趨勢推斷,並改進了現有的 NAND 單元技術。該公司預計,NAND 芯片密度將在三年內達到 100 Gbit/mm2,存儲單元層數為 1,000。要實現這一目標,增長率必須保持在每年1.33 倍。

至於三星方面,韓國科學技術院 (KAIST) 的研究人員此前曾展示其關於使用 Hafnia 鐵電體作為 1,000 層以上 QLC NAND 的「關鍵推動因素」的研究成果,這將是非揮發性存儲領域的分水嶺成就,這也被認為是三星可能的技術方向。

正如 Wccftech所指出的,對 Hafnia 鐵電體的研究具有開創性,而且距離實現仍需數年時間,因為儘管研究仍在進行中,但該技術尚未完全被理解。然而,如果它被證明足夠可靠,可以取代現有技術,那麼它就可以製造出更小的電子元件。儘管三星沒有直接參與這項研究,但據報道,從事這項研究的團隊與三星是一致的。據信,如果取得足夠的成果,他們所做的工作將在某個時候直接轉移到三星的實驗室。

然而,擴展到四位數的層數並非易事。據存儲新聞網站Blocks & Files稱,使用 3D NAND 實現更高密度不僅僅是在芯片上添加更多層。每層都需要一個暴露的邊緣來實現存儲單元之間的連接,從而形成階梯狀的芯片輪廓。因此,隨着層數的增加,階梯結構佔用的面積會大幅增加,從而抵消部分密度增益。

為了彌補這一點,內存製造商需要在向 QLC NAND 過渡時縱向和橫向縮小 NAND 單元,與當今的 TLC 技術相比,每個單元可容納 4 位。隨着層的增加,通道電阻和信號噪聲也成為成長的煩惱。

總之,NAND Flash的競爭,方興未艾。