最近,台積電、英特爾和三星這些領先晶圓代工廠正在2納米上開始激烈競爭。來自日本Rapidus也躍躍欲試。從市場上的報道看來,幾家巨頭的技術各有千秋。雖然台積電實力雄厚,但追趕者(尤其是英特爾不甘人後)。

然而,在2nm還沒有大規模量產之際,市場上已經有了很多1納米技術的新分享。我們綜合一下,以饗讀者。

光刻機,未雨綢繆

衆所周知,要發展先進工藝,光刻機是不可或缺的。在本周,ASML 和 Imec 本周宣佈建立了一項為期五年的合作伙伴關係,旨在使 Imec 的研究人員和開發人員能夠使用 ASML 的最新工具。

報道指出,此舉專注於 2nm 以下工藝技術,這些技術將需要 ASML 最新的光刻技術(包括高數值孔徑)、計量和檢測工具。Imec 將確保來自學術界和各公司的工程師擁有用於研究的最新設備,而 ASML 將確保其工具被整合到尖端工藝技術中。

根據該合作伙伴關係,Imec 將獲得 ASML 全面的先進晶圓製造設備 (WFE),包括頂級 Twinscan NXT (DUV)、Twinscan NXE(具有 0.33 數值孔徑光學器件的Low NA EUV 工具)和 Twinscan EXE(具有 0.55 數值孔徑光學器件的高HighNA EUV 工具)光刻系統。此外,Imec 將在其設施中整合 ASML 的 YieldStar 光學計量解決方案和 HMI 的單光束和多光束檢測工具。

這些工具將安裝在比利時 Imec 的試驗線上,並納入歐盟和Flemish資助的 NanoIC 試驗線。

ASML 的最新一代設備將用於開發下一代半導體生產技術,特別是 2nm 以下的製造技術。人們認為,為了在 2nm 以下的製造節點上實現高效製造,光刻工具必須支持單次曝光 8nm 的分辨率,而這隻有 High-NA EUV 工具才能實現。然而,每台 High-NA EUV 系統的成本高達 3.5 億美元,這使得新玩家或研究人員無法獲得。

ASML 和 Imec 的研究人員之前主要在位於荷蘭費爾德霍芬的 ASML 專用研究設施中使用高 NA(0.55 NA EUV)工具。ASML 在其自己的場地安裝了這些第一代High NA EUV 機器,用於初步測試、評估以及與 Imec 和其他合作伙伴的合作研究。

現在,根據新協議,Imec 將在其位於比利時魯汶的研究線內直接現場使用高 NA 設備,特別是在其最先進的試驗設施以及歐盟和Flemis資助的 NanoIC 試驗線中。這標誌着 Imec 研究人員首次可以在自己的設施內直接使用高 NA EUV 技術,這將加快他們的工作速度。

向 Imec 提供High NA EUV 技術使用權是下一代 7A 項目 (IPCEI22201) 的一部分,並由荷蘭政府作為歐洲共同利益重要項目 (IPCEI) 提供資助。

台積電將建設 1nm超級晶圓廠

與此同時,早前消息披露,台積電已經在台灣組件團隊,加快1納米研發。公司也計劃在台灣建設1納米的超級晶圓廠。

據台灣《聯合報》在2月的報道,全球最大芯片代工廠台積電計劃在台灣南部建設一座1納米工藝工廠,旨在搶在三星電子、英特爾等競爭對手之前推出備受期待的1納米工藝,以鞏固其市場領導地位。

納米(nm)是指半導體芯片上的電路線寬度。線寬越小,功耗越低,處理速度越快,是生產高性能芯片的關鍵因素。儘管台積電此前已宣佈其 1 納米工藝計劃,但這是其首次透露有關其生產線位置和規模的具體細節。

報道,台積電最先進的 1 納米晶圓廠計劃在台南沙崙建設。該廠將建成一座大型 Giga-Fab,容納六條生產線。據報道,該公司已向台灣南部科學園區管理局 (STSPA) 提交了沙崙 1.4 納米和 1 納米生產設施的土地使用申請。前三座晶圓廠(P1 至 P3)將生產 1.4 納米芯片,後三座晶圓廠(P4 至 P6)將專注於 1 納米芯片。該計劃可能會在以後修改,以包括 1 納米和 0.7 納米工藝。

台積電開始在台灣生產 2 納米芯片,並在美國亞利桑那州工廠生產 4 納米芯片。

隨着人工智能芯片需求的激增,代工廠之間的競爭也愈演愈烈。直到去年,3 納米工藝仍主導着先進半導體市場,但台積電和三星電子都計劃今年量產 2 納米芯片。

台積電打算提前推出 1 納米工藝,以保持其在半導體市場的領先地位。該公司最初計劃在 2027 年推出 1.4 納米工藝,但去年,它將時間表提前了一年,並宣佈計劃在 2026 年開始使用 1.6 納米工藝生產半導體。三星電子和英特爾預計將在 2027 年推出 1.4 納米工藝。

1納米的光罩,也啓動了

去年12月,日本印刷株式會社(DNP)宣佈,成功實現了支持半導體制造尖端工藝極紫外 (EUV) 光刻的第一代 2 納米(nm:10 -9米)以上邏輯半導體光掩模所需的精細圖案分辨率。

DNP 還完成了與高數值孔徑2兼容的光掩模標準評估,該應用正在考慮用於 2nm 以後的下一代半導體,並已開始向半導體開發聯盟、製造設備製造商和材料製造商供應評估光掩模。高數值孔徑 EUV 光刻技術可以在硅芯片上形成比以前更高分辨率的精細圖案,並有望實現高性能、低功耗的半導體。

近年來,使用EUV光源的EUV光刻技術在尖端邏輯半導體的量產方面取得了進展,在存儲器半導體領域的應用也不斷擴大,EUV光刻技術已成為尖端半導體供應中不可或缺的技術。

DNP於2023年3月完成了3nm代EUV光刻技術的光掩模製造工藝的開發,並於2024年作為分包商參與了國家研究開發機構——新能源和工業技術發展組織(NEDO)的後5G信息和通信系統基礎設施強化研發項目。

目前,DNP已實現2nm以後邏輯半導體用EUV光刻掩模版所需的精細圖案分辨率,並完成了支持High-NA的EUV光掩模版的開發,該光掩模版被考慮用於2nm以後的下一代半導體,並已完成EUV光掩模版的標準評估,並開始提供樣品掩模版。

DNP表示,要實現2nm以後EUV光刻的光掩模版,需要的圖案比3nm要小20%。這不僅指圖案的大小和形狀,還包括在同一掩模版表面解析各種精細圖案的技術。這不僅包括標準的直線和矩形圖案,還包括越來越複雜的曲面圖案。DNP在成熟的3nm製程工藝基礎上,通過反覆改進,已經達到了2nm以後所需的圖案分辨率。

DNP進一步指出,High NA-EUV光刻的光掩模要求比標準EUV光刻的光掩模更高的精度和更精細的加工。DNP建立並優化了與傳統EUV光刻光掩模不同的製造工藝流程。

DNP表示,公司將繼續建立生產技術,例如提高製造產量,目標是在 2027 財年開始大規模生產第 2nm 代邏輯半導體的光掩模。

我們還將繼續與總部位於比利時魯汶的國際尖端研究機構imec合作,推動光掩模製造技術的發展,着眼於1nm代。

1nm的路線圖回顧

回看集成電路產業的發展,在2022年,Imec就公布了1nm的晶體管路線圖。

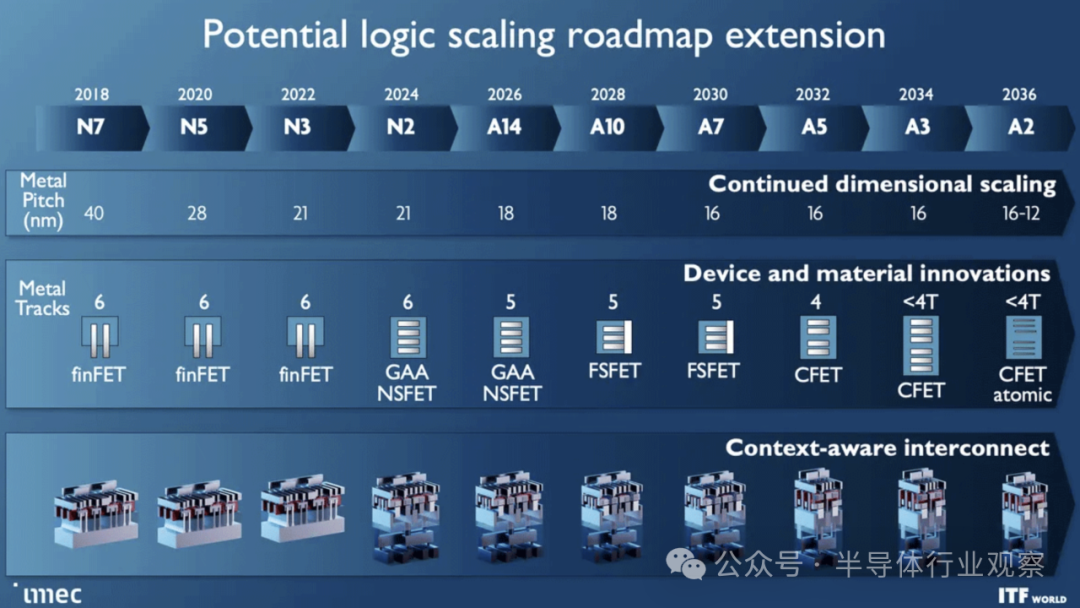

據介紹,路線圖包括突破性的晶體管設計,從持續到 3 納米的標準 FinFET 晶體管發展到 2 納米和 A7(七埃)的新型全柵極 (GAA) 納米片和叉片設計,隨後是 A5 和 A2 的 CFET 和原子通道等突破性設計。提醒一下,10 埃等於 1 納米,因此 Imec 的路線圖涵蓋低於「1 納米」的工藝節點。

下圖展示了新型晶體管的路線圖,這種晶體管將進一步實現密度擴展,並有望實現一些性能改進。全柵 (GAA)/納米片晶體管將在 2nm 節點首次亮相,取代為當今尖端芯片供電的 FinFET。我們已經看到幾家芯片製造商發布了採用這種晶體管技術的不同變體的公告,例如英特爾的四片 RibbonFET。

Imec 預計 GAA/nanosheet 和 forksheet 晶體管(最基本的層次是 GAA 的更密集版本)將持續到 A7 節點。互補 FET (CFET) 晶體管將在 2032 年左右問世時進一步縮小佔用空間,從而允許更密集的標準單元庫。最終,我們將看到具有原子通道的 CFET 版本,這將進一步提高性能和可擴展性。

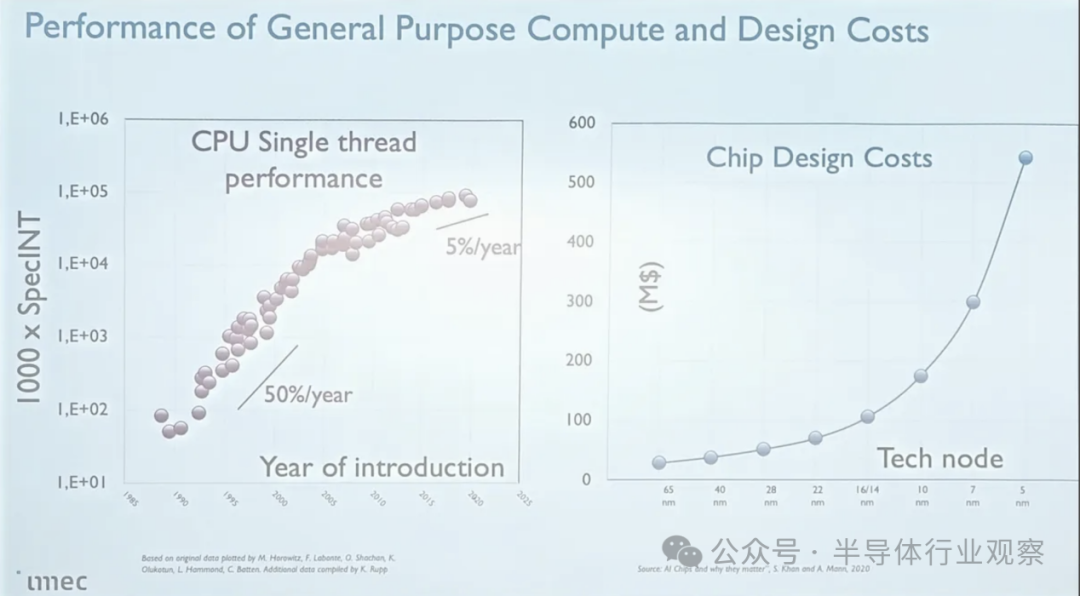

隨着節點的進步、成本的飆升以及對更多計算能力的需求(特別是機器學習的需求)呈非線性增長,該行業面臨着越來越多的挑戰。但Imec完全相信摩爾定律在提出 50多年後仍然有效,儘管我們認為這並不適用於該定律的經濟部分,該部分也定義了隨着時間的推移每個晶體管的成本降低。

事實上,如下圖所示,由於更復雜的設計規則和更長的設計周期時間,芯片設計成本正在飆升,導致每個晶體管的成本增加。此外,單線程性能增益從 90 年代末和 21 世紀初每年 50% 的驚人增幅放緩到每年約 5%。但是,如果我們不考慮密度或經濟因素,摩爾定律通常仍按每兩年翻一番的規律運行。

Imec指出,雖然對更多計算能力的需求過去每兩年翻一番,基本上與摩爾定律帶來的性能提升一致,但機器學習/人工智能所需的原始計算能力大約每六個月翻一番。這是一個令人惱火的問題,因為即使晶體管數量繼續翻番也無法跟上步伐。為此Imec 認為,尺寸縮放(包括更好的密度和封裝技術)、新材料和設備架構以及系統技術協同優化(SCTO)的三管齊下的解決方案可以讓行業保持正軌。

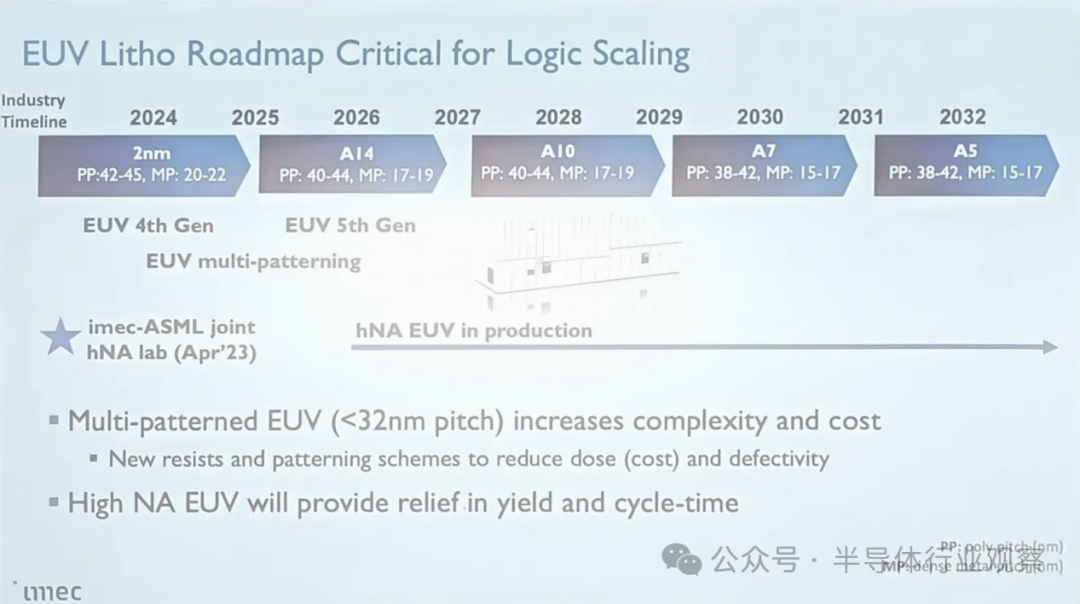

Imec認為,第一步是啓用下一代工具。當今的第四代 EUV 光刻機的孔徑為 0.33,因此芯片製造商必須使用多重圖案化技術(每層曝光一次以上)來創建 2nm 及以下的最小特徵。由於單層晶圓必須「打印」兩次,因此出現缺陷的可能性更高。這將導致產量降低和周期(生產)時間延長,從而導致成本增加。

下一High高 NA 型號(第五代)的孔徑將為 0.55。這種更高的精度將允許在一次曝光中創建更小的結構,從而降低設計複雜性並提高產量、周期時間(每小時 200 片以上晶圓)和成本。Imec 和 ASML 預計這些工具將在 2026 年投入量產。

正如您在最後兩張圖片中看到的,標準 DUV 將我們帶到了 100 MTr/mm2(每平方毫米兆晶體管數量,密度測量),而今天的 0.33NA 將推動行業達到 ~500 MTr/mm2。即將到來的高 NA 機器將需要達到 2nm 才能將其提高到 ~1000 MTr/mm2,並且可能通過多重圖案化超越。

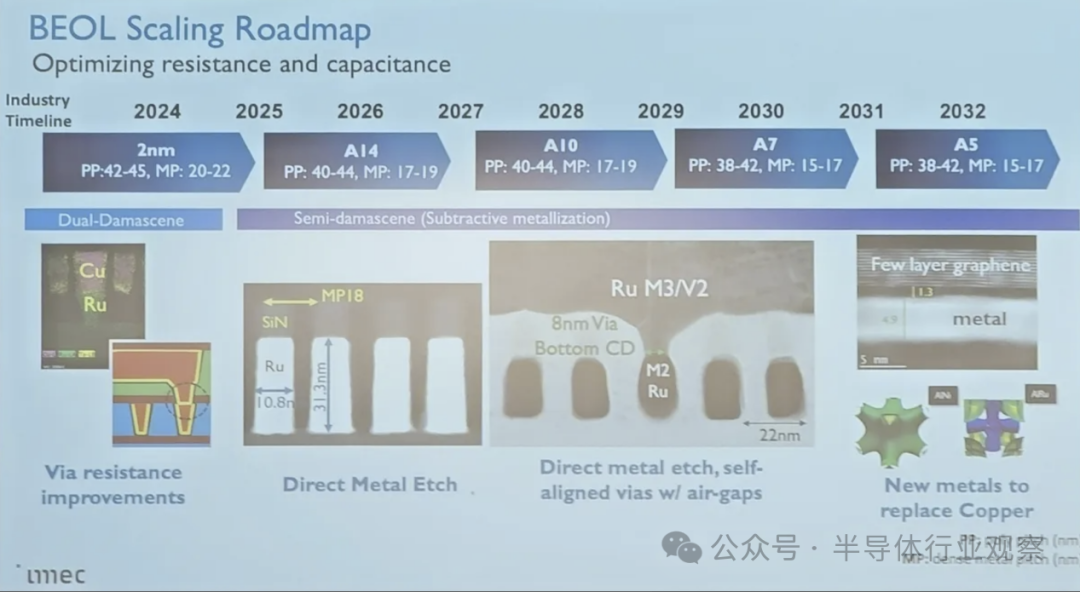

在imec看來,進一步提高晶體管密度和性能特徵還需要增強後端線 (BEOL) 工藝。BEOL 步驟專注於將晶體管連接在一起,從而實現通信(信號)和電力傳輸。Imec將這些二次密度改進技術稱為「縮放助推器」,因為它們有助於提高晶體管密度和性能,即使它們與晶體管的尺寸/位置沒有直接關係。

背面供電是一項關鍵進步,可將電源帶到芯片背面。將電源電路和數據承載互連分開可改善電壓下降特性,從而實現更快的晶體管切換,同時在芯片頂部實現更密集的信號路由。信號傳輸也受益,因為簡化的路由可以實現更快的線路,同時降低電阻和電容。Imec 堅信背面供電將擴展到所有尖端芯片。

當然,熱量可能會成為背面供電的一個問題,因為晶體管將在通常散熱的硅片側面放置金屬層。不過,imec表示,所使用的金屬(目前是銅)足夠擅長散熱,可以減少影響。然而,需要進行一些設計考慮以適應這種技術。

路線圖上的進一步改進包括用於互連的直接金屬蝕刻技術,以及帶有氣隙的自對準通孔。互連,即實現電力傳輸和通信的微型導線,已成為規模化的最大障礙之一。隨着時間的推移,這個問題變得越來越明顯——這些導線的寬度只需要幾個原子厚。Imec 還在研究將取代銅的新金屬,石墨烯就是候選材料之一。

Imec 還在研究系統技術協同優化 (SCTO) 技術,例如 3D 互連和 2.5D 小芯片實現。3D 芯片設計電子設計自動化 (EDA) 軟件的缺乏是阻礙該技術在行業廣泛採用的主要因素。Imec 正在與 Cadence 合作,開發可簡化 3D 設計流程的先進軟件。

展望 2030 年以後,我們看到,imec 預計新材料將取代硅,二維原子通道也將出現。Imec 還認為,隨着行業不可避免地轉向量子計算,基於磁性的柵極可能會成為一種替代方案。