IT之家 4月9日消息,根據首爾經濟日報報道,三星電子開始研發1.0nm晶圓代工工藝,以圖在與台積電的競爭中實現「技術翻盤」。

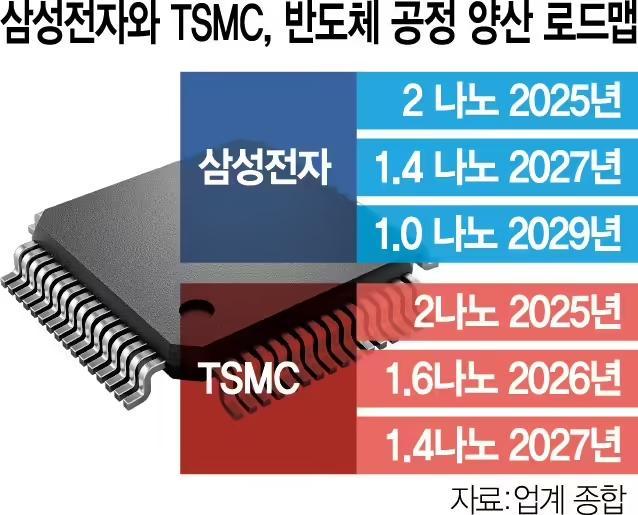

▲ 三星、台積電預測路線圖,圖源首爾經濟日報

根據該日報報道,三星電子半導體研究所近日正式着手研發1.0nm工藝,部分曾參與2nm等尖端製程的研發人員被抽調,組建了專項項目團隊。在目前三星公開的晶圓代工工藝路線圖中,計劃於2027年量產的1.4nm工藝為目前最尖端的工藝。

根據該日報所述,1nm工藝需要打破現有設計框架,引入新技術概念,以及引入高數值孔徑極紫外(High-NA EUV)曝光設備等下一代設備。三星預計,量產時間將在2029年之後。

目前,三星在量產中的3nm工藝,以及預計在今年量產的2nm工藝,首爾經濟日報認為技術上仍落後於台積電,尤其是2nm工藝方面,台積電的良率已突破60%,存在顯著差距。因此,三星對1nm工藝寄予厚望,三星會長李在鎔上月向高管們強調要「延續重視技術的傳統」,並表示「以前所未有的技術引領未來」。

根據IT之家此前援引韓媒The Bell報道,三星目前最新的2nm SF2工藝初始良率「高於預期」,搭載該工藝的Exynos 2600芯片試產良率為30%。